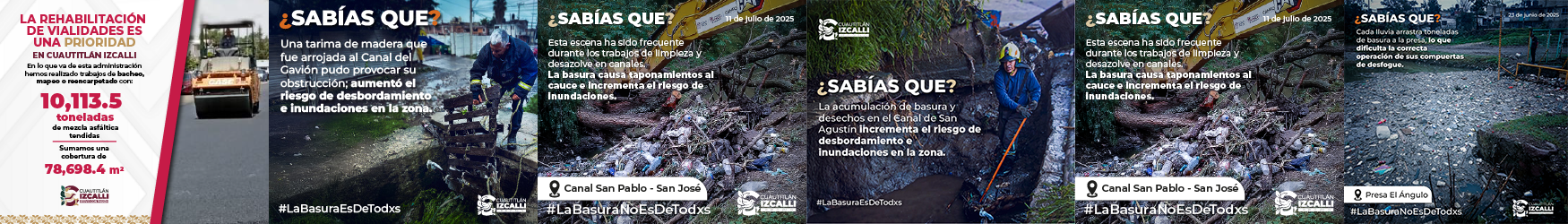

Huawei ha cumplido su promesa: ha encontrado la forma de disparar la competitividad de China en IA frente a EEUU

Hace dos días os contamos algo interesantísimo: el medio estatal chino Securities Times había desvelado que Huawei estaba a punto de presentar un avance tecnológico que perseguía reducir la dependencia de China de los chips de memoria HBM (High Bandwidth Memory) procedentes del extranjero. Según esta fuente Huawei iba a dar a conocer oficialmente su hito tecnológico unas horas después, durante la celebración en Shanghái (China) del Foro de Aplicaciones y Desarrollo de Razonamiento de IA Financiera 2025.

Huawei ha cumplido lo prometido, aunque no tal y como habíamos previsto. En cualquier caso, antes de meternos en harina es importante que recordemos que los fabricantes chinos de chips de memoria no están produciendo soluciones capaces de competir con las memorias más avanzadas que fabrican las compañías surcoreanas Samsung y SK Hynix, o la estadounidense Micron Technology. Las GPU para IA trabajan codo con codo con los chips de memoria HBM. De hecho, su rendimiento está en gran medida condicionado por estas memorias.

Como explican los editores de SemiAnalysis, el ancho de banda total de los chips de memoria HBM3 que conviven con algunas de las GPU para IA más avanzadas de NVIDIA o AMD supera los 819 GB/s, mientras que las memorias DDR5 y GDDR6X alcanzan unos mucho más modestos 70,4 GB/s y 96 GB/s. Las memorias HBM3E y las futuras HBM4 son aún mejores. Los fabricantes chinos de este tipo de chips no producen aún esta clase de memorias, pero parece que Huawei va a alterar profundamente este escenario.

Un algoritmo diseñado expresamente para acelerar la inferencia en IA

La filtración que se produjo hace escasamente 48 horas sugería que probablemente lo que iba a presentar Huawei era una tecnología de empaquetado de vanguardia que, quizá, rivalizaría con las empleadas por SK Hynix, Samsung o Micron para producir sus memorias HBM3 y 3E. Y es que fabricar estos circuitos integrados es complejo debido a que requieren apilar varios chips DRAM e implementar una interfaz entre la XPU (eXtended Processing Unit) o unidad de procesamiento extendido y los chips HBM extraordinariamente densa. Como muestra un botón: en una pila HBM3E la XPU y la memoria HBM están enlazadas a través de más de 1.000 conductores.

Según Huawei el algoritmo UCM es capaz de acelerar drásticamente la inferencia en los grandes modelos de IA

Sin embargo, finalmente Huawei ha presentado una tecnología diferente: un avanzado algoritmo denominado UCM (Unified Cache Manager) que, según esta compañía, es capaz de acelerar drásticamente la inferencia en los grandes modelos de inteligencia artificial (IA). Un apunte relevante: la inferencia es a grandes rasgos el proceso computacional que llevan a cabo los modelos de lenguaje con el propósito de generar las respuestas que corresponden a las peticiones que reciben.

Para lograr su propósito el algoritmo UCM despliega una estrategia muy ingeniosa: decide en qué tipo de memoria es necesario almacenar cada dato tomando como indicador fundamental los requisitos de latencia. En la práctica este algoritmo se comporta como una caché gigantesca que garantiza que cada dato irá a parar a la memoria adecuada, incluida la HBM3, con el propósito de minimizar la latencia durante la inferencia. Si se trata de un dato utilizado con mucha frecuencia se almacenará en una memoria muy rápida, como la HBM3. Según Huawei, esta tecnología es capaz de reducir la latencia de la inferencia en un 90%. Curiosamente, esta compañía planea hacer el algoritmo UCM de código abierto en septiembre.

Más información | SCMP

En Xataka | EEUU quiere acabar con los chips para IA chinos que se venden en el extranjero. Y China sabe cómo defenderse